AVX-512指令集,曾经是Intel的杀手锏,但是随着12代酷睿引入大小核混合架构,E核无法支持AVX-512,不得不整体屏蔽,反倒是AMDZen4架构加入了AVX-512,形势瞬间逆转。

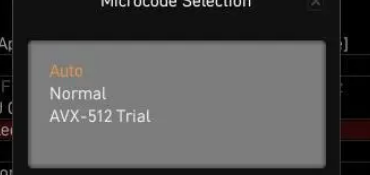

现在,Intel公布了全新的“APX”(高级性能执行),以及全新的指令集“AVX10”(高级指令扩展10),第一次可以让P大核、E小核都支持AVX-512!

基本层面上,大核可以完整执行256/512位指令,小核则只能执行融合256位指令(可以粗略理解为支持到AVX-256)。

更深层面上,AVX10可以说是AVX-512的超集,不但包含所有的AVX-512指令,对应的功能标识为AVX-512VL,还有256位的矢量寄存器、八个32位的掩码寄存器、支持嵌入式舍入的新版256位指令。

其中,P大核可以可以使用512位矢量,E小核则限制在256位矢量长度。

AVX10推出后,AVX-512也将彻底冻结,不会再有变化,未来对于它的使用都通过AVX10来实现。

Intel强调,现有应用基于AVX-512、AVX10的性能是一样的,至少在同等矢量长度下没有区别。

AVX2编译的程序,重新编译支持AVX10,会获得性能提升,且无需再次对软件调优。

对矢量寄存器压力敏感的AVX2程序,获得的性能提升最明显,这要感谢额外的16个矢量寄存器和新的指令。

高度线程化的矢量化应用在E核上运行时,可获得更高的总吞吐量。

Intel下一代消费级酷睿处理器是MeteorLake,依然不会有AVX-512,再下一代的ArrowLake是否会首次加入AVX10,尚不确认。

今年底,Intel将推出第五代可扩展至强EmeraldRapids,只是现有第四代SapphireRapids的升级版,因此要到明年的第六代至强GraniteRapids,才会加入AVX10。

至于明年首款纯小核设计的SierraForest,是否也会加入AVX10,暂时不清楚。

不过,AVX10的落地分为两步,第一步是AVX10.1,用于六代至强GraniteRapids,仅支持512位矢量指令,而不支持融合256位矢量指令。

第二步是AVX10.2,应该用于七代至强ClearwaterForest,加入融合256位矢量指令,并加入其他新功能,比如AI数据类型和转换、数据转移优化等等。